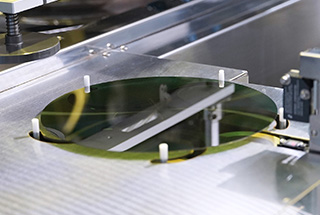

在半導體制造領域,晶圓背面減薄工藝已成為實現集成電路小型化和提升性能的關鍵步驟。這一技術不僅推動了半導體產業的進步,還深刻影響了消費電子、汽車電子及物聯網(IoT)設備的發展。本文將深入探討晶圓背面減薄的優勢與挑戰,以期為相關領域的研究者和從業者提供參考和啟示。

晶圓背面減薄的優勢

1. 提升散熱效率

隨著芯片集成度的不斷提高,晶體管數量急劇增加,散熱已成為影響芯片性能和壽命的關鍵因素。晶圓背面減薄有助于熱量更有效地從襯底導出,顯著提升芯片的散熱效率。薄的芯片結構能夠減小熱阻,使熱量更快速地傳遞至封裝體外部,從而保持芯片在較高性能下的穩定運行。這對于高性能計算和存儲需求尤為重要,能夠有效避免因過熱而導致的性能下降和壽命縮短。

2. 減小封裝體積

在微電子產品日益向輕薄短小方向發展的趨勢下,晶圓背面減薄成為實現這一目標的關鍵技術。通過減薄晶圓,可以顯著減小芯片的封裝體積,進而降低整個電子產品的尺寸和重量。這不僅滿足了消費者對便攜性和美觀性的需求,還為設計師提供了更多在有限空間內優化布局的可能性,提升了產品的整體性能和用戶體驗。

3. 降低內部應力

晶圓厚度減薄還有助于減少芯片工作過程中產生的內部應力。較厚的晶圓在受熱時,背面會產生較大的內應力,隨著溫度升高,基體層之間的熱差異性加劇,進一步加大了內應力,可能導致芯片破裂。而減薄后的晶圓能夠有效降低這種應力,提高芯片的可靠性和耐用性。

4. 提高電氣性能

晶圓背面減薄后,背面鍍金使地平面更接近電路層,從而改善了器件的高頻性能。這種結構變化有助于降低信號傳輸過程中的損耗,提高信號質量和傳輸速率。對于高速通信和數據處理應用而言,這是至關重要的優勢。

5. 提高劃片加工成品率

晶圓減薄還能夠減輕封裝劃片時的加工量,避免劃片中產生崩邊、崩角等缺陷,降低芯片破損的概率。這不僅提高了劃片加工的成品率,還減少了材料浪費,降低了生產成本。

然而,晶圓背面減薄工藝也面臨著一定的挑戰。首先,減薄過程中可能會引入新的缺陷,如劃傷、裂紋等,這要求工藝控制必須非常精確。其次,減薄后的晶圓在后續加工和封裝過程中需要更加細致的處理,以避免因脆性增加而導致的破損。此外,晶圓背面減薄技術的成本也是一大考量因素,包括設備投資、工藝優化及良品率提升等方面的成本。

為了克服這些挑戰,研究者們正不斷探索新的減薄技術和工藝優化方案。例如,采用先進的化學機械拋光(CMP)技術,可以在保證減薄效果的同時,減少表面缺陷的產生。同時,通過引入先進的檢測設備,可以實時監控減薄過程中的質量變化,確保最終產品的可靠性。

未來,隨著半導體技術的不斷發展,晶圓背面減薄工藝將扮演更加重要的角色。它不僅將繼續推動集成電路的小型化和性能提升,還將為新興領域如人工智能、5G通信等提供強有力的技術支持。因此,我們有理由相信,在研究者們的共同努力下,晶圓背面減薄工藝將不斷取得新的突破,為半導體產業的繁榮和發展貢獻力量。

?